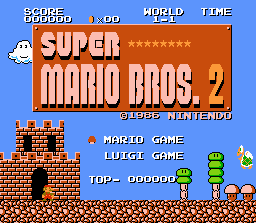

Can you help getting more info about those carts?

| Unique visits: 7902 Can you help getting more info about those carts? |

|  |

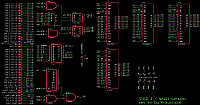

| Name | Value |

|---|---|

| IC1 | 27128 |

| IC2 | 27256 |

| IC3 | 27256 |

| IC4 | 2764 |

| IC5 | 16L8 |

| IC6 | 4020 |

| IC7 | 74139 |

| IC8 | 7400 |

| C1 | 470p |

| CART1 | FAMICOM_CART |

| D1 | |

| D2 | |

| D3 | |

| D4 | |

| D5 | |

| D6 | |

| R1 | 510 |

| R2 | 2.2k |

O1 <=

'0' when (!ASEL0 & CPU_D0 & !CPU_D1 & !CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) else

'1' when (!ASEL0 & !CPU_D0 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL0 & CPU_D1 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL0 & CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL);

O2 <=

'0' when (!ASEL0 & CPU_D0 & CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) else

'1' when (!ASEL0 & !CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL0 & !CPU_D0 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL);

O3 <=

'0' when (!ASEL0 & CPU_D1 & CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) else

'1' when (!ASEL0 & !CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL0 & !CPU_D1 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL);

RESET <=

'0' when (!ASEL1 & CPU_D0 & CPU_D1 & !CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) else

'1' when (!ASEL1 & !CPU_D1 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL1 & !CPU_D0 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL) |

(!ASEL1 & CPU_D2 & !CPU_RnW & !CPU_A12 & !CPU_A13 & CPU_A14 & CPU_nROMSEL);

IF TAKING CARE RESET IF NOT TAKING CARE RESET

PRG-A13 = (O3 & O2 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | PRG_A13 = (O3 & !O2 & O1 & !CPU_A13) |

(O1 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | (!O3 & O2 & O1 & !CPU_A13) |

(O3 & O2 & !CPU_A13 & !CPU_A14) | | (O3 & O2 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) |

(O3 & O2 & !CPU_A14 & CPU_nROMSEL) | | (O3 & O2 & !O1 & !CPU_A13) |

(O3 & O2 & !CPU_A13 & CPU_nROMSEL) | | (O1 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) |

(O1 & !CPU_A13 & !CPU_A14) | | (O3 & O2 & !CPU_A14 & CPU_nROMSEL) |

(O1 & !CPU_A14 & CPU_nROMSEL) | | (O1 & !CPU_A14 & CPU_nROMSEL) |

(O1 & !CPU_A13 & CPU_nROMSEL); | (O1 & !CPU_A13 & !CPU_A14) |

| (O1 & !CPU_A13 & CPU_nROMSEL);

|

PRGSEL0 = (O3 & O2 & !CPU_A12 & !CPU_A13 & CPU_nROMSEL) | | PRGSEL0 = (O1 & !CPU_A12 & !CPU_A13 & CPU_nROMSEL) |

(O1 & !CPU_A12 & !CPU_A13 & CPU_nROMSEL) | | (O3 & O2 & !CPU_A14 & CPU_nROMSEL) |

(O3 & O2 & !CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | (O1 & !CPU_A13 & CPU_A14 & !CPU_nROMSEL) |

(O3 & O2 & !CPU_A14 & CPU_nROMSEL) | | (O3 & O2 & !CPU_A12 & !CPU_A13 & CPU_nROMSEL) |

(O1 & !CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | (O1 & !CPU_A14 & CPU_nROMSEL);

(O1 & !CPU_A14 & CPU_nROMSEL); |

|

PRGSEL1 = (O3 & O2 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | PRGSEL1 = (O3 & O2 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) |

(O1 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) | | (O1 & CPU_A13 & CPU_A14 & !CPU_nROMSEL) |

(O3 & O2 & !CPU_A14 & CPU_nROMSEL) | | (O3 & O2 & !CPU_A14 & CPU_nROMSEL) |

(O3 & O2 & !CPU_A13 & CPU_nROMSEL) | | (O3 & O2 & !CPU_A13 & CPU_nROMSEL) |

(O1 & !CPU_A14 & CPU_nROMSEL) | | (O1 & !CPU_A14 & CPU_nROMSEL) |

(O1 & !CPU_A13 & CPU_nROMSEL); | (O1 & !CPU_A13 & CPU_nROMSEL);

|

PRG-A14 = (O3 & O2 & CPU_A13 & CPU_A14) | | PRG_A14 = (O3 & O2 & !O1 & CPU_A14) |

(RESET & !O3 & !O2 & O1 & CPU_A14) | | (O3 & O2 & CPU_nROMSEL) |

(O3 & O2 & CPU_nROMSEL) | | (!O2 & O1 & CPU_A14) |

(O1 & CPU_A13 & CPU_A14) | | ( O1 & CPU_nROMSEL) |

(O1 & CPU_nROMSEL); | (O1 & CPU_A13 & CPU_A14);

|

---

R/!W A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

!ASEL0 0 0 0 1 0 0 0 1 0

!ASEL1 1 0 0 1 0 0 0 1 0

O1/O2/O3 0 0 1 0 0 x x x

D2 D1 D0 | O3 O2 O1

0 0 0 | 1 1 1 7

0 0 1 | 1 1 0 6

0 1 0 | 1 1 1 7

0 1 1 | 1 1 1 7

1 0 0 | 1 1 1 7

1 0 1 | 1 0 1 5

1 1 0 | 0 1 1 3

1 1 1 | 0 0 1 1

Memory map:

$5000 | $6000 | $7000 | $8000 | $9000 | $a000 | $b000 | $c000 | $d000 | $e000 | $f000

$11 $4 $5 $2 $3 $0 $1 {$4022} {$4022} $12 $13

+ 1

Registers:

$4022 [.... ..PPP] - set PRG bank, note that this reg is scrambled so that:

written value at D2-D0: 0 1 2 3 4 5 6 7

value latched at O3-O1: 7 6 7 7 7 5 3 1

bank set to $c000 : $8 $6 $8 $8 $8 $e $a $c

$4122 [.... ..III] - enable (3) or disable+ack (0/1/2/4/5/6/7) interrupt

When enabled, interrupt is triggered after 4096 rising edges of M2 (when not acked, it will be

automatically acked after another 4096 rising edges)

0000

1000

2000

3000

4000

5000 17

6000 4

7000 5

8000 2

9000 3

a000 0

b000 1

c000 1=>12 3=>10 5=>14 6=>6 7=>8

d000 1=>13 3=>11 5=>15 6=>7 7=>9

e000 18

f000 19

done

Comments:

| Bob: | 2023-04-21 03:41:28 |

| Hello Krzysiobal Can you create a JED file? This is too difficult for me. | |