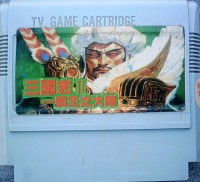

Can you help getting more info about those carts?

| Unique visits: 7831 Can you help getting more info about those carts? |

|  |

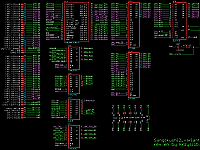

| Name | Value |

|---|---|

| IC1 | 27F080 |

| IC2 | 27F080 |

| IC3 | AX5208C(VRC4) |

| IC4 | 74157 |

| IC5 | 74174 |

| IC6 | 74157 |

| IC7 | 16L8 |

| IC8 | 6264 |

| BAT | CR2032 |

| CART1 | FAMICOM_CART |

| D1 | |

| R1 | 2.2k |

| R2 | 4,7k |

http://forum.contrabanda.eu/index.php?topic=855.msg12531#msg12531

http://forums.nesdev.com/viewtopic.php?f=9&t=19364#p243092

Like that:

[url=https://obrazki.elektroda.pl/7344712300_1570580645.png][img]https://obrazki.elektroda.pl/7344712300_1570580645_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/8343892700_1570580626.png][img]https://obrazki.elektroda.pl/8343892700_1570580626_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/2137067500_1570580627.png][img]https://obrazki.elektroda.pl/2137067500_1570580627_thumb.jpg[/img][/url]

I see great simiarity to [url=https://forums.nesdev.com/viewtopic.php?f=9&t=19041&start=0]this[/url]

They used /WR_9003 pin of VRC

It is generally regular VRC with modifications:

* VRC_A1 <- CPU_A11, VRC_A0 <- CPU_A10 making registers sits at $x000/$x400/$x800/$xc00, instead of $x000/$x001/$x002/$x003

* high 4 bits of CHR registers are moved from D3..D0 into D7..D4

* There is additional register that latches PRG bank (PAL decides when it is applied). Probably at $c000.

CPU PPU

$8000 $A000 $C000 $E000 | $0000 $0400 $0800 $0C00 $1000 $1400 $1800 $1C00

------------------------+------------------------------------------------

| $B000 $B800 $C000 $C800 $D000 $D800 $E000 $E840

$8000 $A000 $9C00 -1 | + + + + + + + +

| $B400 $BC00 $C400 $CC00 $D400 $DC00 $E400 $EC00

-> $8000 (mask: $FC00)

fedcba9876543210 76543210

A~[100000..........] D~[..PPPPPP]

mask 1111110000000000 ||||||

++++++- PRG bank select at $8000-$9fff

-> $A000 (mask: $FC00)

fedcba9876543210 76543210

A~[101000..........] D~[..PPPPPP]

mask 1111110000000000 ||||||

++++++- PRG bank select at $a000-$bfff

-> $B000/$B400/$B800/$BC00/$C000/$C400/$C800/$CC00/$D000/$D400/$D800/$DC00/$E000/$E400/$E800/$EC00 (mask: $FC00)

fedcba9876543210 76543210 fedcba9876543210 76543210

A~[1*****..........] D~[....LLLL] A~[1*****..........] D~[HHHH....]

mask 1111110000000000 |||| mask 1111110000000000 ||||

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $0000-$03ff ($B000+$B400)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $0400-$07ff ($B800+$BC00)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $0800-$0bff ($C000+$C400)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $0c00-$0fff ($C800+$CC00)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $1000-$13ff ($D000+$D400)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $1400-$17ff ($D800+$DC00)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $1800-$1bff ($E000+$E400)

++++------------------------------++++-- HHHHLLLL = 1kb CHR bank at $1c00-$1fff ($E800+$EC00)

-> $9C00 (mask: $FC04)

fedcba9876543210 76543210

A~[100111.......0..] D~[...QQQQQ]

mask 1111110000000100 |||||

+++++- PRG bank select at $c000-$dfff

-> $9C04/$9C05/$9C06/$9C07 (mask: $FC07)

fedcba9876543210 76543210

A~[100111.......1**] D~[.......M]

mask 1111110000000111 |

+- select single screen mirroring:

$9c04: at $2000-$23ff

$9c05: at $2400-$27ff

$9c06: at $2800-$2bff

$9c07: at $2c00-$2fff

-> $F000 (mask: $FC00): IRQ Latch, low 4 bits

-> $F400 (mask: $FC00): IRQ Latch, high 4 bits

-> $F800 (mask: $FC00): IRQ Control

-> $FC00 (mask: $FC00): IRQ AcknowledgeComments: