Flintstones (J)

Elements:

Chip signature:

27F080+27F080+74157+DIL64

PCB top:

PCB bottom:

Shell top:

Shell bottom:

Screenshoots:

No photo

Extra info:

https://www.crazysmart.net.au/phpBB3/viewtopic.php?f=10&t=3

This board is found in The Flintstones: The Rescue of Dino & Hoppy for the Famicom. Is is likely that Captain Saver, Bubble Bobble 2 and The Jetsons also use the TC0690.

--

I bought original Flintstones to test the TC0690 chip.

On real hardware (NTSC console) Flintstones run fine. I swapped the EPROMs for the ones with pre-programmed Jetsons ROMs and there is the scanline artifact (see attached videos).

Flintstones: https://youtu.be/fdR8Reo8xFU

Jetsons: https://youtu.be/eQ64sxrECQI

[url=https://obrazki.elektroda.pl/6156020100_1564691943.jpg][img]https://obrazki.elektroda.pl/6156020100_1564691943_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/9513056300_1564691946.jpg][img]https://obrazki.elektroda.pl/9513056300_1564691946_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/1569856900_1564691947.jpg][img]https://obrazki.elektroda.pl/1569856900_1564691947_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/6340000100_1564691991.png][img]https://obrazki.elektroda.pl/6340000100_1564691991_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/8156423400_1564700625.png][img]https://obrazki.elektroda.pl/8156423400_1564700625_thumb.jpg[/img][/url]

---

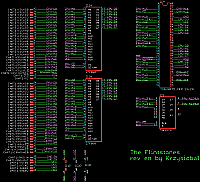

The TC0690 pinout on this particular cartridge is following.

[code]

_____

n/c -- /01 64\ -- n/c

n/c -- /02 63\ -- n/c

CHR A15 <- /03 (o) 62\ -> CHR A16

PPU /RD <- /04 61\ -> CHR A11

CHR A18 <- /05 60\ -- n/c

CHR A10 <- /06 59\ -- GND

PPU A12MUX -> /07 58\ <- CPU D3

PPU A11 -> /08 57\ -- VCC

VCC -- /09 56\ <- CPU D2

PPU A10 -> /10 55\ <- CPU D4

GND -- /11 54\ <- CPU D1

CHR A13 -> /12 53\ <- CPU D5

PPU A13MUX -> /13 TAITO TC0690FMI 52\ -- n/c

CHR A14 <- /14 51/ -- n/c

CHR A12 <- /15 50/ -- n/c

CIRAM A10 <- /16 49/ -- n/c

CHR A17 <- /17 48/ <- CPU D0

n/c -- /18 47/ <- CPU A1

n/c -- /19 46/ <- CPU D6

n/c -- \20 45/ <- CPU A0

/IRQ <- \21 44/ <- CPU D7

/ROMSEL -> \22 43/ -- GND

PRG /CE <- \23 42/ -> CHR /CE

CPU R/W -> \24 41/ -- VCC

VCC -- \25 40/ <- M2

PRG A15 <- \26 39/ -- n/c

GND -- \27 38/ -> PRG A17

PRG A13 <- \28 37/ <- CPU A13

CPU A14 -> \29 36/ -> PRG A18

PRG A16 <- \30 35/ -> PRG A14

n/c -- \31 34/ -- n/c

n/c -- \32 33/ -- n/c

\ /

\ /

[/code]

I was particulary curious about the huge amount of unconnected pins, so:

* 1, 2, 18, 19, 20, 31, 32, 33, 34, 39, 49, 50, 51, 52, 60, 63, 64 - no signs of any internal connection (multimeter diode test to GND/VCC)

* 5 - CHR A18 (because TC0690 does not ignore D0 unlike MMC3 when setting 2k CHR banks, it is possible to access 512kB CHR memory but only using 2k banks)

* 36 - PRG A18

--

IRQ seems to behave differently that in the MMC3:

[code]

048 - MMC3

---------------

$C000 $C000 irq latch

$C001 $C001 irq reload

$C002 $E001 irq en

$C003 $E000 irq dis

[/code]

* Mechanism of IRQS:

[code]

if falling_edge(PPU_/RD)

if PPU_A13 = 0 AND LAST_PPU_A12 = 1 AND PPU_A12 = 0

if (IRQ_counter = 255)

IRQ_pending <= 1;

end if;

IRQ_counter++;

end if;

LAST_PPU_A12 <= PPU_A12

end if

[/code]

* IRQ is asserted immediatelly if IRQ_pending flag is set AND IRQs_are_enabled

* It is impossible to tell if the IRQ_counter is reloaded instantly when writing to C001 or when falling edge of PPU /RD (but that does not matter)

* Only writing to C001 clears the IRQ_pending flag (dislabling IRQs doesn't)

* IRQ counter reacts only when there is a PPU A12 transition at $0000-$1fff and only during PPU reads (because the external 74157 mux prevents chip from seeing actual PPU A12/A13 values during PPU write cycles)

* IRQ counter does not checks for M2 when determining if two A12 transitions are too close to each other

[url=https://obrazki.elektroda.pl/8674828600_1564700311.png][img]https://obrazki.elektroda.pl/8674828600_1564700311_thumb.jpg[/img][/url]

Comments:

Want to leave a comment?