Zanac (FDS port)

| Type | single | | Mapper | | | Original mapper | | | PCB marks | 09-034A ~A~ | | Tags: | #fds | | Uploaded: | 2019-09-21 12:36:42 |

|  |

Elements:

Chip signature:

6264+27128(27512)+27256(27512)+7432+74138+7474+74138+7432

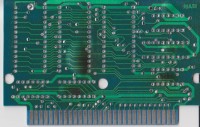

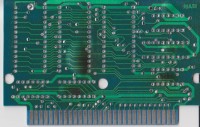

PCB top:

PCB bottom:

Shell top:

No photo

Shell bottom:

No photo

Screenshoots:

No photo

Extra info:

https://forums.nesdev.com/viewtopic.php?f=9&t=18336

https://wiki.nesdev.com/w/index.php/NES_2.0_Mapper_304

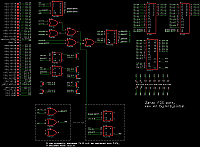

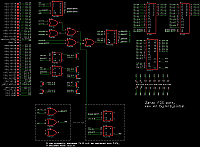

The PCB looks extremely weird, not only because it has chips soldered on the bottom side (like only in original famicom games), but mainly because there are many:

* vias-to-nowhere (which might be jumpers), weird traces (which also could be jumpers and ned to be cut)

[url=https://obrazki.elektroda.pl/7132656300_1569144655.png][img]https://obrazki.elektroda.pl/7132656300_1569144655_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/5796840600_1569144708.png][img]https://obrazki.elektroda.pl/5796840600_1569144708_thumb.jpg[/img][/url]

* stupid connections, probably they wanted to make some universal cartridge:

[url=https://obrazki.elektroda.pl/6092206800_1569144746.png][img]https://obrazki.elektroda.pl/6092206800_1569144746_thumb.jpg[/img][/url]

* is it place for for DIP20 chip?

[url=https://obrazki.elektroda.pl/9409172600_1569145111.png][img]https://obrazki.elektroda.pl/9409172600_1569145111_thumb.jpg[/img][/url]

* Currently, $8000-$ffff points to unbanked PRG1 (27256, 32K) and $6000-$7fff to PRG2 (27128, 16K), while the PRG2-A13 is selected by $4027.0 (mask: $ec7f), with bus conflicts

* If JP3 is switched from 2-3 to 1-2 and PRG2 from 27128 to 27256, $4020.0 (mask: $ec7f) can control PRG2-A14

* CHR-RAM can be replaced with 27128/27256 and when JP6 is switched from 1-3 to 2-3, then it can be banked either using $4027.0 or $4020.0 (depending on JP4/JP5/JP6)

* Currently with IC4=7432 it is weird (output of IC4.11 is shorted to output of IC7.13) and IRQ is also driven to VCC with this gate. However, if IC4 is replaced with 7474 then $4022.1 can control /IRQ line. Still stupid, but at least electrically correct - I would rather expect some 4020 counter that counts M2 edges which asserts /IRQ.

And the currently valid connection for IC4A will be broken. This gate is not needed - if they connected CPU-R/W to IC5.1, exchanged IC5.9 with IC5.7 and moved IC5.11 to IC8.10, the functionality would retain the same and even there would be no more bus-conflicts.

[url=https://obrazki.elektroda.pl/8148349200_1569069692.jpg][img]https://obrazki.elektroda.pl/8148349200_1569069692_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/7608095100_1569069695.png][img]https://obrazki.elektroda.pl/7608095100_1569069695_thumb.jpg[/img][/url]

Comments:

Want to leave a comment?