12 in 1

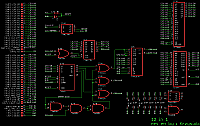

Elements:

Chip signature:

27F080+6264A+74174+74161+74153+74139+7400+7432

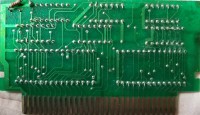

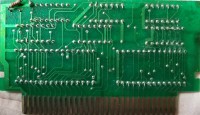

PCB top:

PCB bottom:

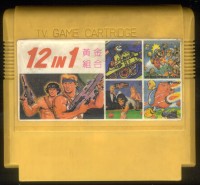

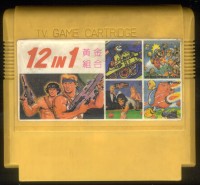

Shell top:

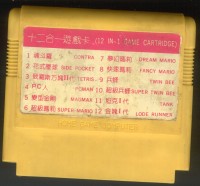

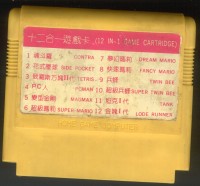

Shell bottom:

Screenshoots:

Extra info:

first write | second write

addr hex bin | addr hex bin

-------------------+--------------------

tetris $c000 $04 00000100 | $8000 $68 01101000 V

pacman $c000 $04 00000100 | $8000 $ea 11101010 H

magmax $c000 $05 00000101 | $8000 $ec 11101100

super mario $c000 $05 00000101 | $8000 $6e 01101110

fancy mario $c000 $05 00000101 | $8000 $ee 11101110

twin bee $c000 $06 00000110 | $8000 $c8 11001000

battle city $c000 $06 00000110 | $8000 $8a 10001010

lode runner $c000 $07 00000111 | $8000 $0b 00001011

contra $c000 $00 00000000 | $8000 $30 00110000

side pocket $c000 $00 00000000 | $8000 $90 10010000

contra=3 = prg03

sidepocket=1 = prg04

tetr/pac/mag=2 = prg02

twink bee/menu=0 = prg01

PRG01.nes =

0 => PRG 25 Japan\TwinBee (J).nes

1 => PRG 22 Japan\TwinBee (J).nes

2 => PRG 83 Japan\Battle City (J).nes

3 => PRG 8 Japan\Lode Runner (J).nes

4a=> CHR 0 Unlicensed\Tetris (Unl) (U) [p1].nes

4b=> CHR 0 USA\Ms Pac-Man (U).nes

5a=> CHR 2 Japan\Magmax (J).nes

5b=> CHR 70 Unclassified\ZZZ_UNK_w256 (40976).nes

6a=> CHR 115 Japan\TwinBee (J).nes

6b=> CHR 130 Japan\Battle City (J).nes

7a=> CHR 10 USA\Lode Runner (U).nes

7b=> MENU

PRG02.nes =

0 => PRG 90 Unlicensed\Tetris (Unl) (U) [p1].nes

1 => PRG 1063 Unlicensed\Tetris (Unl) (U) [p2][!].nes

2 => PRG 0 USA\Ms Pac-Man (U).nes

3 => PRG 5 USA\Ms Pac-Man (U).nes

4 => PRG 23 Japan\Magmax (J).nes

5 => PRG 2 Japan\Magmax (J).nes

6 => PRG 17 Unclassified\ZZZ_UNK_w256 (40976).nes

7 => PRG 8 Unclassified\ZZZ_UNK_2600 Bros (SMB1 Hack) (UNL).nes

PRG03.nes = contra (unrom, mirr=v)

PRG04.nes = side pocket (unrom, mirr=h)

------------------------------------

Order of combining: PRG03 + PRG04 + PRG02 + PRG01

PRG-ROM: 512 kB (hovewer A19 is wired to the EPROM)

CHR-RAM: 8 kB

[mvPP .P..] 74*174: $8000-$bfff

|||| |

||++--+--- outer PRG (high to low: D0, D5, D4)

|+-------- mode (0=16kB, 1=32kB)

+--------- mirroring (0=V, 1=H)

[.... uppp] 74*161: $8000-$9fff and $c000-$dfff

||||

|+++- inner PRG

+---- mode (0=UNROM,1=NROM)

yes, it overlaps partially with previous reg, so when wring at $8000-$9fff, both registers are updated

Power up: both registers set to 0

Reset: no change

PRG Modes:

uv $8000 $bfff

----------------

00 PPPppp PPP111

01 PPPpp0 PPP111

10 PPPppp PPPppp

11 PPPpp0 PPPpp1

------------------------------------

#include "mapinc.h"

static uint8 reg174, reg161;

//shifts bit at position `from` to position `to` in expression

#define shi(exp, from, to) ((((exp) >> (from)) & 1) << (to))

static SFORMAT StateRegs[] =

{

{ 0 }

};

static void Sync(void) {

int uv = shi(reg161, 3, 1) | shi(reg174, 6, 0);

int PPP = shi(reg174, 0, 2) | shi(reg174, 5, 1) | shi(reg174, 4, 0);

int ppp = reg161 & 0x7;

switch (uv) {

case 0: setprg16(0x8000, (PPP << 3) | ppp); setprg16(0xc000, (PPP << 3) | 7); break;

case 1: setprg16(0x8000, ((PPP << 3) | ppp) & (~1)); setprg16(0xc000, (PPP << 3) | 7); break;

case 2: setprg16(0x8000, (PPP << 3) | ppp); setprg16(0xc000, (PPP << 3) | ppp); break;

case 3: setprg32(0x8000, ((PPP << 3) | ppp) >> 1); break;

}

setmirror(((reg174 >> 7) & 1) == 0 ? MI_V : MI_H);

}

static DECLFW(M281Write) {

if ((A >= 0x8000) && (A <= 0xBFFF)) {

reg174 = V;

}

if (((A >= 0x8000) && (A <= 0x9FFF)) || ((A >= 0xC000) && (A <= 0xFFFF))) {

reg161 = V;

}

Sync();

}

static void M281Power(void) {

setchr8(0);

reg174 = reg161 = 0;

SetWriteHandler(0x8000, 0xffff, M281Write);

SetReadHandler(0x8000, 0xFFFF, CartBR);

Sync();

}

static void M281Reset(void) {

Sync();

}

static void StateRestore(int version) {

Sync();

}

void Mapper281_Init(CartInfo *info) {

info->Power = M281Power;

info->Reset = M281Reset;

GameStateRestore = StateRestore;

AddExState(&StateRegs, ~0, 0, 0);

}

Comments:

Want to leave a comment?