?

Elements:

| Name | Value |

|---|

| IC1 | 6264 |

| IC2 | 28F016 |

| IC3 | 6264 |

| IC4 | TINY13 |

| IC5 | XC9572 |

| BAT1 | CR2032 |

| C1 | ? |

| C2 | ? |

| C3 | ? |

| C4 | ? |

| C5 | ? |

| C6 | ? |

| C7 | ? |

| C8 | ? |

| CART1 | NES_CART |

| D1 | |

| D2 | |

| D3 | |

| JP1 | |

| R1 | 27k |

| R2 | 2.2k |

| R3 | ? |

| R4 | ? |

| T1 | ? |

| VREG1 | LD1117-3.3 |

Chip signature:

6264+28F016+6264+TINY13+XC9572

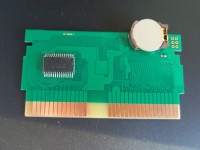

PCB top:

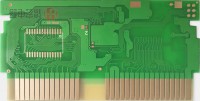

PCB bottom:

Shell top:

No photo

Shell bottom:

No photo

Screenshoots:

No photo

Extra info:

https://forums.nesdev.com/viewtopic.php?f=9&t=20962

http://www.jinhongpcb.cn/jinshouzhi/16912848.html

https://fr.aliexpress.com/item/4000639521092.html?spm=a2g0s.9042311.0.0.166e6c373VSN7z

This is that PCB rev-en. CPLD chip indeed is XC9536 (or XC9572) in VQ44 package.

It inputs:

* CPU-D0..D7,CPU-A14,13,12,9,8, R/W, /ROMSEL, M2

* PPU-A13..A10, PPU /RD

[code]

-----CPU-A------

111111

5432109876543210

**** **

0101000000000000 $5000

0101000100000000 $5100

0101001000000000 $5200

0101001100000000 $5300

[/code]

It has enough input address lines for mapper 163.

But because it does not take PPU-A9 into account for automatic mid-screen pattern table switch, either it produces garbage title screen (what I doubt) or it counts scanlines, either by PPU-A13 or PPU-A12 (which is more probable because of the cap at PPU-A12) to find out the exact moment when to switch. That way it require few more macrocells for counter, but it should fit into 64 without problem - this mapper needs really little bits to store.

Comments:

Want to leave a comment?