Cosmic Spacehead

Elements:

| Name | Value |

|---|

| U1 | 27F080 |

| U2 | 6264 |

| U3 | CME-01(DIL28) |

| C1 | 10u/16V |

| C2 | 100u/6.3v |

| C3 | 100n |

| C4 | 47p |

| C5 | 47p |

| CART1 | NES_CART |

| D1 | 1N4004 |

| D2 | 1N4004 |

| R1 | 220R |

| R2 | - |

| R3 | 10k |

| T1A | ? |

| T1B | IRLD120 |

| X1 | 10.0M |

Chip signature:

27F080+6264+CME-01(DIL28)

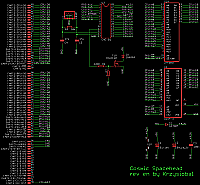

PCB top:

PCB bottom:

Shell top:

No photo

Shell bottom:

No photo

Screenshoots:

Extra info:

Codemaster' CME-01 and Cosmic Spacehead rev-eng

I've got [url=http://bootgod.dyndns.org:7777/profile.php?id=4588]Cosmic Spacehead[/url] for testing. This is the only known game that contains Codemasters' CME-01 DIP28 chip. This is remastered Aladdin version of `Linus Spacehead Cosmic Crusade`, with the following differences (maybe there more):

* Cosmic Spacehead is dated 1993, while LSCC is 1992 (this is in fact the only NES Codemasters game dated 1993, others are 1992 or 1991)

* Cosmic Spacehead uses new Codemasters logo

* The splash screen is different

* There is something called "2 player pie slap" in Cosmic Spacehead

* Plus the shell shape looks very different from standard NES shells.

Linus Spacehead Cosmic Crusade:

[url=https://obrazki.elektroda.pl/9384055600_1583332702.png][img]https://obrazki.elektroda.pl/9384055600_1583332702_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/9528879800_1583332705.png][img]https://obrazki.elektroda.pl/9528879800_1583332705_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/4389509300_1583332706.png][img]https://obrazki.elektroda.pl/4389509300_1583332706_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/1434594100_1583332708.png][img]https://obrazki.elektroda.pl/1434594100_1583332708_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/3776916500_1583332709.png][img]https://obrazki.elektroda.pl/3776916500_1583332709_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/4556185600_1583332711.png][img]https://obrazki.elektroda.pl/4556185600_1583332711_thumb.jpg[/img][/url]

Cosmic Spacehead:

[url=https://obrazki.elektroda.pl/2832860000_1583332730.png][img]https://obrazki.elektroda.pl/2832860000_1583332730_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/5384002600_1583332731.png][img]https://obrazki.elektroda.pl/5384002600_1583332731_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/2829202900_1583332734.png][img]https://obrazki.elektroda.pl/2829202900_1583332734_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/3616635100_1583332735.png][img]https://obrazki.elektroda.pl/3616635100_1583332735_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/2355635600_1583332737.png][img]https://obrazki.elektroda.pl/2355635600_1583332737_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/3616794600_1583332740.png][img]https://obrazki.elektroda.pl/3616794600_1583332740_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/9369831000_1583332743.png][img]https://obrazki.elektroda.pl/9369831000_1583332743_thumb.jpg[/img][/url]

About the mapper and chip:

[code]

.----v----.

(R) PRG-A16 <- | 01 28 | -- +4.3V

(R) PRG-A15 <- | 02 27 | -> PRG A17 (R)

(R,N) CPU-A12 -> | 03 26 | -> PRG A14 (R)

(N) CPU-A14 -> | 04 25 | <- CPU A13 (R,N)

(N) CPU /RMS -> | 05 24 | -> PRG /CE (R)

(N) CIC+RST -> | 06 23 | -> PRG /OE (R)

(N) CPU R/W -> | 07 22 | <- CPU D7 (R,N)

(n/c) OUTER2 <- | 08 21 | <- CPU D0 (R,N)

(n/c) OUTER0 <- | 09 20 | <- CPU D6 (R,N)

(n/c) OUTER1 <- | 10 19 | <- CPU D1 (R,N)

MOSFET <- | 11 18 | <- CPU D5 (R,N)

10MHz CLK IN -> | 12 17 | <- CPU D2 (R,N)

10MHz CLK OUT <- | 13 16 | <- CPU D4 (R,N)

GND -- | 14 15 | <- CPU D3 (R,N)

'---------'

* Mapper is clocked with external 10MHz ceramic resonator (blue thing)

* There is 4 bit inner PRG bank, like in mapper 71: [....pppp] at $c000-$ffff

* There is 3 bit outer PRG bank, like in mapper 232: [...PPP..] at $8000-$bfff

(with one additional bit) ||+---- pin 9

|+----- pin 10

+------ pin 8

* Pin 23 = PRG /OE <= /ROMSEL or not CPU-R/W

* Pin 24 = PRG /CE <= '1' when copy_protection_enabled else '0'

Reading $0000-$ffff while copy protection is enabled returns $EA)

* After power up, copy protection is enabled. To disable it, CIC+RST must become low,

and then - CPU read from $f000-$ffff must happen. If CIC+RST is floating, game won't work.

* For current state of knowledge, CPU D7/D6/D5 do not seem to affect anything

* Above chip and PRG-ROM are powered from +4.3V (1n4004 diode in series with +5V)

* Pin 11 controls N-mosfet. If it goes high, it can cause very high current to flow from VCC to GND.

However, I wasn't able to toggle this pin high.

[/code]

[url=https://obrazki.elektroda.pl/2076021200_1583339729.png][img]https://obrazki.elektroda.pl/2076021200_1583339729_thumb.jpg[/img][/url] [url=https://obrazki.elektroda.pl/5457693900_1583334212.jpg][img]https://obrazki.elektroda.pl/5457693900_1583334212_thumb.jpg[/img][/url] Comments:

Want to leave a comment?