Downtown Special Kunio-kun no Jidaigeki Dayo Zenin Shuug

| Type | single | | Mapper | | | Original mapper | | | PCB marks | NONE | | Tags: | | | Uploaded: | 2018-01-29 01:35:10 |

|  |

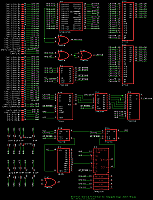

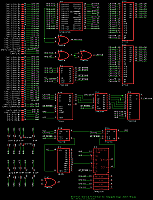

Elements:

Chip signature:

74138+27512+27512+7474+4020+74193+NTDEC8701+74259+74161+74151+7402

PCB top:

PCB bottom:

Shell top:

No photo

Shell bottom:

No photo

Screenshoots:

No photo

Extra info:

http://forum.pegasus-gry.com/index.php/topic,7281.msg68830.html#msg68830

Kilka lat temu pozyskałem ciekawe pcb bez obudowy. Niestety, gra jest uszkodzona. Już na pierwszy rzut oka widać, że mamy do czynienia z nietypowym „hardware”. Na początek chciałem odczytać dane z prom-ów PRG oraz CHR aby ustalić tytuł gry. Pamięć PRG posiadała wewnętrzne zwarcie w układzie scalonym, a więc odczyt był niewykonalny i ujawniła się przyczyna niesprawności. Kość z grafiką jakoś udało się skopiować. Analiza danych zajęła trochę czasu, ale było warto poznać tajemniczy tytuł; Downtown Special Kunio-kun no Jidaigeki Dayo Zenin Shuugou

http://images.tinypic.pl/i/00957/q6bdjert7jyx.jpg

http://images.tinypic.pl/i/00957/8j9cxq155143.jpg

---------------------------------------------

This is MIMIC-1 mapper (MMC3 predecessor) with modified (inverted) PRG-A16, added seventh bit to CHR register to control CHR-A16 and added IRQs.

Mirroring is hardwired to V.

Original MICIC-1

$8000 (mask: $E001): Bank select

7 bit 0

---- ----

xxxx xRRR

|||

+++- Specify which bank register to update on next write to Bank Data register

0: Select 2 KB CHR bank at PPU $0000-$07FF

1: Select 2 KB CHR bank at PPU $0800-$0FFF

2: Select 1 KB CHR bank at PPU $1000-$13FF

3: Select 1 KB CHR bank at PPU $1400-$17FF

4: Select 1 KB CHR bank at PPU $1800-$1BFF

5: Select 1 KB CHR bank at PPU $1C00-$1FFF

6: Select 8 KB PRG ROM bank at $8000-$9FFF

7: Select 8 KB PRG ROM bank at $A000-$BFFF

-------------------------------------------------

$8001 (mask: $E001): Bank data

7 bit 0

---- ----

xxdd DDDd

|| ||||

++-++++- New bank value, based on last value written to bank select register (mentioned above)

Only five bits exist for the two 2 KiB CHR banks, only six bits exist for the four 1 KiB CHR banks, and only four bits exist for the two 8 KiB PRG banks.

PRG-A16 from mapper is inverted, so it maps like:

PRG memory:

$8000 | $a000 | $c000 | $e000

----------+----------+----------+----------

$8000.reg6|$8000.reg7| |

xor | xor | 6 | 7

0b1000 |0b1000 | |

CHR memory:

$0000 | $0800 | $1000 | $1400 | $1800 | $1c00

----------------------+---------------------+----------+----------+----------+----------

$8000.reg0 | $8000.reg1 |$8000.reg2|$8000.reg3|$8000.reg4|$8000.reg5

IRQ mechanism:

There is 4 bit counter, which is decreased by one every 1024 edge of M2. When it reaches 0, IRQ is fired.

IRQ can be acknowledged by writing to $e000 or when counter rolls from 0 to 15 (which will occur after 1024 edges of m2)

$e000 (mask: $e003): writing any value holds counter in reset and acknowledges pending IRQ

$e002 (mask: $e003): writing any value releases counter from reset

$c000 (mask: $e001): writing sets counter value to d3..d0

Comments:

Want to leave a comment?